# MAINTAINING PLATFORM FLEXIBILITY USING A MODEL-BASED SOFTWARE DESIGN APPROACH

Alexander Wirthmüller aw@mpsitechnologies.com

## Introduction

#### About me

- Based in Munich

- Diploma in Electrical Engineering

- R&D Engineer at Mynaric (FPGA-based error-correction algorithms for free-space optical laser communications)

- Founder and Director at MPSI Technologies

- MPSI Technologies: make Embedded Software development more fun by replacing repetitive tasks by model-based source code generation

# Making a case for platform flexibility

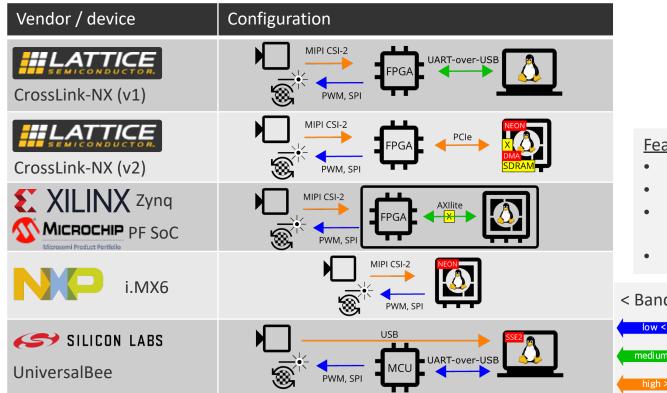

#### Silicon device landscape

- Increasing number of contenders

- Specific strengths, can be:

- Low static / dynamic power consumption

- "Extra" features such as DSP blocks or high-performance or PHY-specific I/O's

- The right size / attractive price point

- Competition for FPGA-typical functionality from CPU's featuring vector extensions / SIMD

#### Application landscape

- Requirements are not written in stone, architectures need to adapt, e.g.:

- 100Mbit/s vs. 1Gbit/s Ethernet

- 1 megapixel vs. 5 megapixel camera modules

- Single-channel vs. multi-channel DSP

- Skillset of available staff can influence FPGA vs. CPU decision making

Hardware variants | Key software functionality

#### **Features**

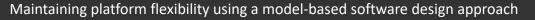

- Turntable with stepper motor

- Tripod with camera/laser holder

- IMX335 MIPI CSI-2 camera (5MP) max. data rate 150MB/s @30fps

- Two adjustable red line lasers

Hardware variants | Key software functionality

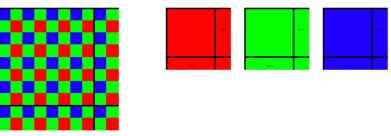

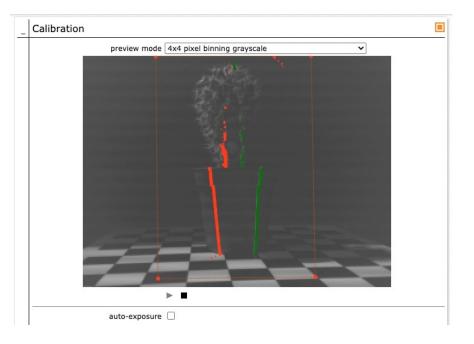

• Preview image acquisition

2560 x 1920 -> 160 x 120 (color)

2048 x 1536 -> 512 x 384 (grayscale)

#### Hardware variants | Key software functionality

- Preview image acquisition

- Checkerboard corner detection for orientation

#### Hardware variants | Key software functionality

- Preview image acquisition

- Checkerboard corner detection for orientation

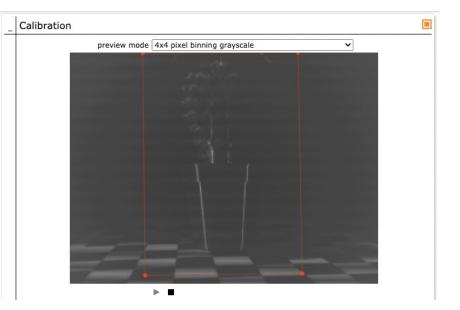

- On/off identification of line laser traces in frames

#### Hardware variants | Key software functionality

- Preview image acquisition

- Checkerboard corner detection for orientation

- On/off identification of line laser traces in frames

each algorithm can be performed

→ either on the Linux host or on the FPGA, ← with varying load on the interconnect

ightarrow yet each one host/FPGA source code tree ightarrow

# Spotlight on FPGA vendor IP 1/3

#### Dual-port RAM | MIPI CSI-2 PHY | Pipelined algorithm

- Most use cases can be covered using few parameters

- Size

- PortA/B widths 8/16/32/64 bits

- PortA/B read- vs. write-only

- Output buffer yes/no

```

Dpram (

[vendor,]

size [kB],

width{A/B}{8/16/32/64},

{rd/wr}only{A/B},

buf{A/B}

)

```

- Route to vendor-independence

- VHDL wrapper with standardized port names

- Give instructions for configuring IP wizards

```

entity Dpram v1 0 size58kB is

port (

clkA: in std logic;

enA: in std logic;

weA: in std logic;

aA: in std logic vector(15 downto 0);

drdA: out std logic vector(7 downto 0);

dwrA: in std logic vector(7 downto 0);

clkB: in std logic;

enB: in std logic;

aB: in std logic vector(13 downto 0);

drdB: out std logic vector(31 downto 0)

);

end Dpram v1 0 size58kB;

```

# Spotlight on FPGA vendor IP 2/3 Dual-port RAM | MIPI CSI-2 PHY | Pipelined algorithm

- Silicon capabilities vary significantly

- Lattice: integrated PHY/Decoder IP

- Microchip: IOD IP, PLL and MIPI RX Decoder IP

- Xilinx: SelectIO (from UltraScale+ native MIPI), "MIPI CSI-2 Receiver Subsystem" IP to AXI Stream

- VHDL wrapper with standardized AXI Stream output

Mipirx ( [vendor,] fDDR [MHz], nLane{1,2,4}, res{8,10,12,14}

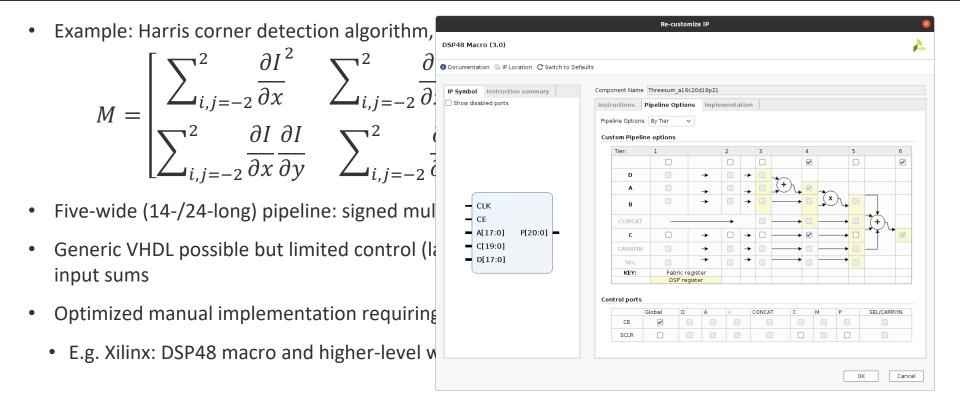

#### Spotlight on FPGA vendor IP 3/3

Dual-port RAM | MIPI CSI-2 PHY | Pipelined algorithm

• Example: Harris corner detection algorithm, matrix formula

$$M = \begin{bmatrix} \sum_{i,j=-2}^{2} \frac{\partial I}{\partial x}^{2} & \sum_{i,j=-2}^{2} \frac{\partial I}{\partial x} \frac{\partial I}{\partial y} \\ \sum_{i,j=-2}^{2} \frac{\partial I}{\partial x} \frac{\partial I}{\partial y} & \sum_{i,j=-2}^{2} \frac{\partial I}{\partial y}^{2} \end{bmatrix}$$

$$R = \det(M) - k \operatorname{trace}(M)^2$$

- Five-wide (14-/24-long) pipeline: signed multiplications and sums/differences

- Generic VHDL possible but limited control (latency, resource usage) for multiplications and threeinput sums

- Optimized manual implementation requiring custom wait cycles

- E.g. Xilinx: DSP48 macro and higher-level wizards "Adder/Subtracter", "Multiplier"

## Spotlight on FPGA vendor IP 3/3

#### Dual-port RAM | MIPI CSI-2 PHY | Pipelined algorithm

### Spotlight on FPGA vendor IP 3/3

#### Dual-port RAM | MIPI CSI-2 PHY | Pipelined algorithm

• Example: Harris corner detection algorithm, matrix formula

$$M = \begin{bmatrix} \sum_{i,j=-2}^{2} \frac{\partial I}{\partial x}^{2} & \sum_{i,j=-2}^{2} \frac{\partial I}{\partial x} \frac{\partial I}{\partial y} \\ \sum_{i,j=-2}^{2} \frac{\partial I}{\partial x} \frac{\partial I}{\partial y} & \sum_{i,j=-2}^{2} \frac{\partial I}{\partial y}^{2} \end{bmatrix}$$

- Five-wide (14-/24-long) pipeline: signed multiplications and s

- Generic VHDL possible but limited control (latency, resource input sums

- Optimized manual implementation requiring custom wait cy

- E.g. Xilinx: DSP48 macro and higher-level wizards "Adder/S

```

implementation: Harris score pipeline forward opera

process (reset, mclk, stateFwd)

begin

if reset='1' then

elsif rising edge(mclk) then

if stateFwd=stateFwdRun then

if ceScore='1' then

xsqr3p1 <= xsqr(71 downto 54);</pre>

xsqr3p2 <= xsqr3p1;</pre>

xsqr4p1 <= xsqr(89 downto 72);</pre>

xsqr4p2 <= xsqr4p1;</pre>

colsumX4p1 <= colsumX(104 downto 84);</pre>

colsumX4p2 <= colsumX4p1;

colsumX4p3 <= colsumX4p2;</pre>

colsumX4p4 <= colsumX4p3;

diffI IIp1 <= diffI II;</pre>

end if;

end if;

end if:

end process;

```

Layer model | Hardware abstraction | Command invocation | Buffer transfer

|                            | <u>Linux host</u>           | <u>FPGA</u>          |  |  |  |

|----------------------------|-----------------------------|----------------------|--|--|--|

| application layer          | C++ data processing         | RTL algorithms,      |  |  |  |

| application layer          |                             | state machines, etc. |  |  |  |

| application layer handoff  | target-specific             | target module        |  |  |  |

| application layer handon   | C++ API library             | RTL handshake        |  |  |  |

| protocol layer             | encode/decode               | host interface       |  |  |  |

| protocorrayer              | C++ code                    | RTL module           |  |  |  |

| hardware abstraction layer | device driver               | soft IP              |  |  |  |

| physical layer             | silicon IP and copper wires |                      |  |  |  |

| physical layer             | standard-compliant          |                      |  |  |  |

Layer model | Hardware abstraction | Command invocation | Buffer transfer

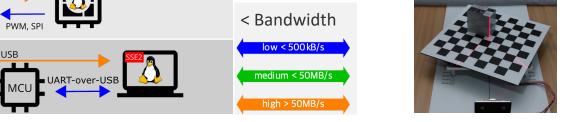

|               | Complexity           | Net bandwidth | Support                               | Conditions                            |

|---------------|----------------------|---------------|---------------------------------------|---------------------------------------|

| UART          | 2 wire               | 400 kB/s      | i.MX6 (all 32/64bit SoC's)            | 4 Mbps on-PCB routing                 |

| UART over USB | 2 wire               | 417 kB/s      | FTDI                                  | x64 host USB2.0 hi-speed,<br>FT232R   |

| SPI           | 3 wire               | 4.8 MB/s      | OMAP3xxx (all 32/64bit SoC's)         | 40 MHz on-PCB routing                 |

| AXIIite       | (on-chip)            | 50 MB/s       | Zynq (all FPGA-SoC's)                 | 32 bit words, 100 MHz clock           |

| PCIe          | 3 diff. pair, 4 wire | 250 MB/s      | CrosslinkNX (all mid-range<br>FPGA's) | one lane PCIe 1.x, 2.5 Gbps           |

| AXI4          | (on-chip)            | 776 MB/s      | PolarFire SoC (all FPGA-SoC's)        | 64 bit x 256 bursts, 100 MHz<br>clock |

#### Layer model | Hardware abstraction | Command invocation | Buffer transfer

- Linux host

- Character device driver (open(), ioctl(), read(), write(), close())

- Easily applicable for UART, SPI, AXIlite

- User I/O API for PCIe and AXI4 with DMA (works with interrupts and callbacks)

- FPGA design

- Generic UART, SPI, AXIlite modules for basic rx/tx(<number of words>)

- PCIe IP by four major vendors free but not Open Source

#### Layer model | Hardware abstraction | Command invocation | Buffer transfer

|                                                   |                                                    | ſ                                              |                                                                         |

|---------------------------------------------------|----------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------|

|                                                   | entity Spislave v1 0 is                            |                                                | entity Axirx_v2_0 is                                                    |

| • RTL module examples                             | generic (                                          | process (extresetn, extclk)                    | port(                                                                   |

| IT E module examples                              | cpol: std logic := '0';                            |                                                | <pre>reset: in std_logic;</pre>                                         |

|                                                   | cpha: std logic := '0';                            | A                                              |                                                                         |

| entity Uartrx_v1_1 is                             | opila. Sta_rogro ,                                 | begin<br>if extresetn='0' then                 | <pre>mclk: in std_logic;</pre>                                          |

| generic(                                          | <pre>nssByteNotXfer: std logic := '0';</pre>       | <pre>stateOp &lt;= stateOpInit;</pre>          |                                                                         |

| fMclk: natural range 1 to 1000000;                | misoPrecphaNotCpha: std logic := '0'               |                                                | req: in std_logic;<br>ack: out std logic;                               |

|                                                   | );                                                 |                                                | <pre>ack: out std_logic;<br/>dne: out std logic;</pre>                  |

| fSclk: natural range 100 to 50000000              | );<br>port (                                       | elsif rising edge(extclk) then                 | ane: out sta_logic;                                                     |

| );                                                | reset: in std logic;                               | if stateOp=stateOpInit then<br>                | <pre>len: in std logic vector(21 downto 0); in words, max. 2^22-1</pre> |

| port (                                            | reset: in sta_logic;                               | <br>stateOp <= stateOpIdle;                    | Ten: In stu_togic_vector(21 downed 0, / In words, max. 2 22 1           |

| reset: in std logic;                              | with the static lands.                             | braccop , thirtypen,                           | d: out std logic vector(31 downto 0);                                   |

|                                                   | <pre>mclk: in std_logic;</pre>                     | elsif stateOp=stateOpIdle th                   | strbD: out std logic;                                                   |

| mclk: in std logic;                               |                                                    | if (axi_bvalid='1' and loc                     |                                                                         |

| morr. in coa_coget,                               | req: in std_logic;                                 | if rdyRx='1'then                               | rdyRx: out std logic;                                                   |

| req: in std logic;                                | <pre>ack: out std_logic;</pre>                     | <pre>enRx &lt;= '1'; end if;</pre>             | enRx: in std_logic;                                                     |

| ack: out std logic;                               | <pre>dne: out std_logic;</pre>                     | end II,                                        | _                                                                       |

| dne: out std logic;                               |                                                    | stateOp <= stateOpWrrdyA                       | <pre>rx: in std_logic_vector(31 downto 0);</pre>                        |

| die. out sta_rogre,                               | <pre>len: in std_logic_vector(16 downto 0);</pre>  |                                                | strbRx: in std_logic                                                    |

| 2 is still light match (16 downto 0).             |                                                    | elsif (axi_bvalid='1' and )                    | );                                                                      |

| <pre>len: in std_logic_vector(16 downto 0);</pre> | <pre>send: in std_logic_vector(7 downto 0);</pre>  | <pre>if rdyTx='1'then    enTx &lt;= '1';</pre> | end Axirx_v2_0;                                                         |

|                                                   | <pre>strbSend: out std_logic;</pre>                | enTx <= 'l';<br>end if;                        |                                                                         |

| <pre>d: out std_logic_vector(7 downto 0);</pre>   |                                                    |                                                |                                                                         |

| <pre>strbD: out std_logic;</pre>                  | <pre>recv: out std_logic_vector(7 downto 0);</pre> | stateOp <= stateOpRdrdyA;                      | ,                                                                       |

|                                                   | <pre>strbRecv: out std_logic;</pre>                | end if;                                        |                                                                         |

| <pre>rxd: in std_logic;</pre>                     |                                                    |                                                |                                                                         |

|                                                   | <pre>nss: in std_logic;</pre>                      | <br>end if;                                    |                                                                         |

| burst: in std_logic                               | <pre>sclk: in std_logic;</pre>                     | end 11;<br>end if;                             | AXIIite                                                                 |

| );                                                | <pre>mosi: in std_logic;</pre>                     | end process;                                   |                                                                         |

| end Uartrx_v1_1;                                  | <pre>miso: inout std_logic</pre>                   |                                                |                                                                         |

|                                                   | );                                                 |                                                |                                                                         |

|                                                   | end Spislave_v1_0;                                 |                                                |                                                                         |

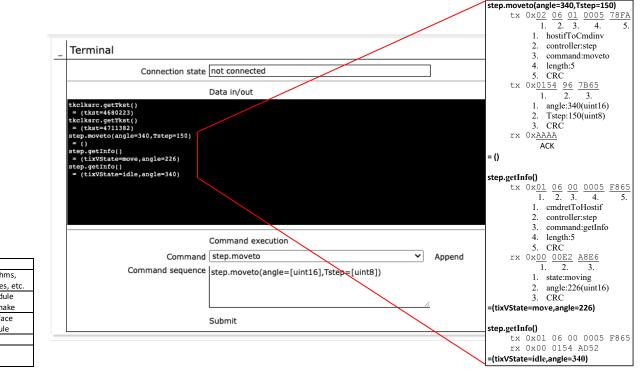

#### Layer model | Hardware abstraction | Command invocation | Buffer transfer

• Host: C++ API library forms byte code and initiates transfers guarded by CRC

ĩ1 0 1

|                            | Linux host                  |     | FPGA            |  |                      |

|----------------------------|-----------------------------|-----|-----------------|--|----------------------|

| application layer          | C++ data processing         |     | RTL algorithms, |  |                      |

| application layer          | , ,                         |     |                 |  | state machines, etc. |

| application layer handoff  | target-specific             |     | target module   |  |                      |

| application layer handon   | C++ API library             |     | RTL handshake   |  |                      |

| protocol layer             | encode/decode               |     | host interface  |  |                      |

| protocoriayer              | C++ code                    |     | RTL module      |  |                      |

| hardware abstraction layer | device driver               |     | soft IP         |  |                      |

| physical layer             | silicon IP and copper wires |     |                 |  |                      |

| physical layer             | standard                    | -co | mpliant         |  |                      |

#### Layer model | Hardware abstraction | Command invocation | Buffer transfer

• FPGA: "host interface" module decodes the byte string and triggers a handshake with the "step" target module

Layer model | Hardware abstraction | Command invocation | Buffer transfer

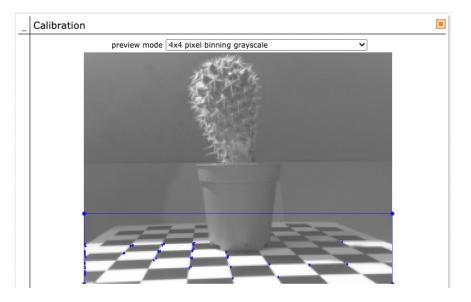

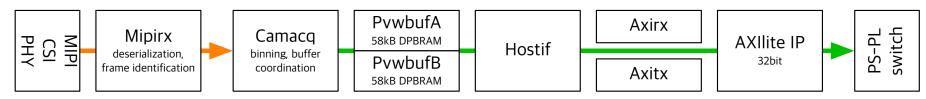

• FPGA: reduce 2560x1920 YUV images @30fps (150MB/s) to 160x120 RGB images (1.73MB/s), then provide to host in A/B buffer

• Host: poll the buffer status, initiate buffer transfer and display

|                            | Linux host                         |   | <u>FPGA</u>                            |  |  |

|----------------------------|------------------------------------|---|----------------------------------------|--|--|

| application layer          | C++ data processing                |   | RTL algorithms,<br>tate machines, etc. |  |  |

| application layer handoff  | target-specific<br>C++ API library |   | target module<br>RTL handshake         |  |  |

| protocol layer             | encode/decode<br>C++ code          |   | host interface<br>RTL module           |  |  |

| hardware abstraction layer | device driver                      | Ψ | soft IP                                |  |  |

| physical layer             |                                    |   | copper wires<br>compliant              |  |  |

Maintaining platform flexibility using a model-based software design approach

#### FPGA Conference Europe 2022

Layer model | Hardware abstraction | Command invocation | Buffer transfer

• FPGA: reduce 2560x1920 YUV images @30fps (150MB/s) to 160x120 RGB images (1.73MB/s), then provide to host in A/B buffer

• Host: poll the buffer status, initiate buffer transfer and display

#### Maintaining platform flexibility using a model-based software design approach

#### FPGA Conference Europe 2022

#### Job tree | Vector extensions

- Use fine granularity for C++ classes, and well-defined interfaces

- Example: user session (preview image) Lattice FPGA vs. Xilinx FPGA-SoC vs. NXP i.MX6

- + RootWzsk

- + SessWzsk

- + CrdWzskLlv

- + PnlWzskLlvCamera

- + JobWzskAcqPreview/S

- + JobWzskAcqFpgapvw/S

- JobWzskSrcClnxevb/S

- + RootWzsk

- + SessWzsk

- + CrdWzskLlv

- + PnlWzskLlvCamera

- + JobWzskAcqPreview/S

- + JobWzskAcqFpgapvw/S

- JobWzskSrcArty/S

- + RootWzsk

- + SessWzsk

- + CrdWzskLlv

- + PnlWzskLlvCamera

- + JobWzskAcqPreview/S

- JobWzskSrcV412/S

- Web UI jobs in blue, communicate over HTTP(S) using JSON/XML

- Preview acquisition job in green, reacts on new frame available and passes it on to web UI job

- FPGA preview job in orange, runs thread polling FPGA preview buffer status and transfers data

- Source jobs in red, interact with FPGA (UART-over-USB vs. AXIIite) vs. with camera using V4L2 API

#### Job tree | Vector extensions

• Decision on which *jobs* to instantiate using global flag

if (xchg->stgwzskglobal.ixWzskVTarget == VecWzskVTarget::ARTY) srcarty = new JobWzskSrcArty(xchg, dbswzsk, jref, ixWzskVLocale); else if (xchg->stgwzskglobal.ixWzskVTarget == VecWzskVTarget::CLNXEVB) srcclnxevb = new JobWzskSrcClnxevb(xchg, dbswzsk, jref, ixWzskVLocale); else if (xchg->stgwzskglobal.ixWzskVTarget == VecWzskVTarget::ICICLE) srcicicle = new JobWzskSrcIcicle(xchg, dbswzsk, jref, ixWzskVLocale); else if (xchg->stgwzskglobal.ixWzskVTarget == VecWzskVTarget::ICICLE) srcicicle = new JobWzskSrcIcicle(xchg, dbswzsk, jref, ixWzskVLocale); else if (xchg->stgwzskglobal.ixWzskVTarget == VecWzskVTarget::MCVEVP) srcmcvevp = new JobWzskSrcMcvevp(xchg, dbswzsk, jref, ixWzskVLocale);

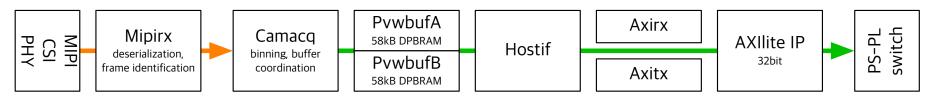

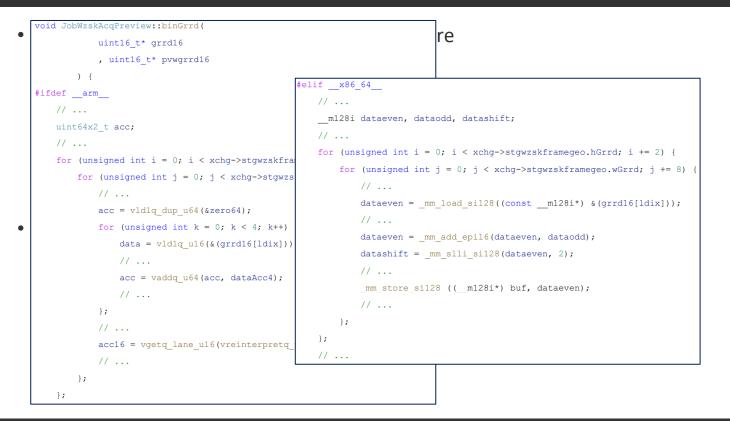

# Spotlight on host software Job tree | Vector extensions

• Use #ifdef guards to determine architecture

```

#ifdef __arm__

#include <arm_neon.h>

#elif __x86_64__

#include <emmintrin.h>

#endif

```

• Grayscale binning for ARM -> intel x64 -> others

#### Job tree | Vector extensions

```

void JobWzskAcgPreview::binGrrd(

re

uint16 t* grrd16

, uint16_t* pvwgrrd16

) {

#ifdef __arm__

11 ...

uint64x2 t acc;

// ...

for (unsigned int i = 0; i < xchg->stgwzskframegeo.hGrrd; i += 4) {

for (unsigned int j = 0; j < xchg->stgwzskframegeo.wGrrd; j += 8)

// ...

acc = vld1q_dup_u64(&zero64);

for (unsigned int k = 0; k < 4; k++) {

ers

data = vld1q u16(&(grrd16[ldix]));

// ...

acc = vaddq u64(acc, dataAcc4);

};

// ...

acc16 = vgetq lane u16(vreinterpretq u16 u64(acc), 0);

// ...

};

};

```

#### Job tree | Vector extensions

#### Job tree | Vector extensions

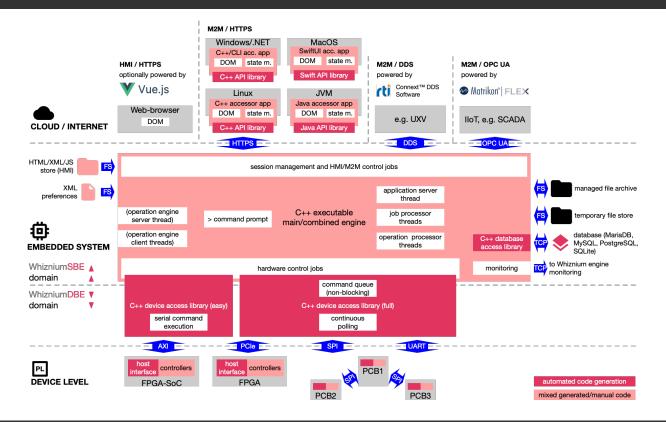

- Coverage of the "Embedded Full Stack"

- WhizniumDBE ("Device Builder's Edition") for FPGA / MCU level and its host access libraries (primary languages: C, VHDL)

- WhizniumSBE ("Service Builder's Edition") for Embedded Linux and "outside world" levels (primary languages: C++, HTML)

- Successive model composition within an SQL database using import (I) and generation (G) steps

- Output of source code trees only thereafter

- Text-based model files ("diffable")

#### WhizniumDBE (Device Builder's Edition)

- Modular structure (I)

- Command set and buffer transfers (I)

- Data flows and algorithms (I)

- Fine structure (G)

- Custom fine structure (I)

- Finalization (G)

#### WhizniumSBE (Service Builder's Edition)

- Deployment information (I)

- Global features (I)

- Database structure (I)

- Basic user interface structure (I)

- Import/export structure (I)

- Operation pack structure (I)

- Custom jobs (I)

- User interface (G)

- Custom user interface features (I)

- Job tree (G)

- Custom job tree features (I)

- Finalization (G)

• Module definition, command definition, fine structure

#### Overview | Composition | Example

| lexWdbeM  |                       |                 |                                    |             |             |                |               | <u> </u> |

|-----------|-----------------------|-----------------|------------------------------------|-------------|-------------|----------------|---------------|----------|

| ImelMUnit | srefSilRefWdbeMUnit   | sref            | Title                              | Easy        | srefKToolch | Comment        |               |          |

| fpga      | mpfs250t-fcvg484      | iccl            | Microchip PolarFire Soc Icicle kit | true        | libero      |                |               |          |

|           | ImeIMModule.srefixVBa | hsrefSupRefWdl  | srefTplRefWdbeMModule              | sref        | Comment     |                |               |          |

|           | wrp                   |                 | mpfs_ip_AXI_v1_0                   | iccl_ip_AXI |             |                |               |          |

|           | top                   | iccl_ip_AXI     | top_mchp_v1_0                      | top         |             |                |               |          |

|           |                       | ImelAMModule    | Val                                |             |             |                |               |          |

|           |                       | fExtclk         | 125000                             |             |             |                |               |          |

|           |                       | extresetNNotP   | true                               |             |             |                |               |          |

|           |                       | ImelAMModule    | Par.end                            |             |             |                |               |          |

|           |                       | ImelMGeneric.s  | Defval                             |             |             |                |               |          |

|           |                       | fMclk           | 50000                              |             |             |                |               |          |

|           |                       | ImelMGeneric.e  | nd                                 |             |             |                |               |          |

|           |                       |                 |                                    |             |             |                |               |          |

|           | ectr                  | iccl_ip_AXI;top |                                    | step        | stepper mot | or control (28 | BYJ-48 via UL | N2003)   |

|           |                       |                 |                                    |             |             |                |               |          |

|           | ImeIMModule.end       |                 |                                    |             |             |                |               |          |

| melMUnit. | end                   |                 |                                    |             |             |                |               |          |

#### Overview | Composition | Example

| lexW  | dbeCsx v1.1.9       |        |                          |                           |                    |              |            |          |             |                        |                           |

|-------|---------------------|--------|--------------------------|---------------------------|--------------------|--------------|------------|----------|-------------|------------------------|---------------------------|

| Imell | MUnit.sref          |        |                          |                           |                    |              |            |          |             |                        |                           |

| iccl  |                     |        |                          |                           |                    |              |            |          |             |                        |                           |

|       | ImeIMModule.hsrefSu | p sref |                          |                           |                    |              |            |          |             |                        |                           |

|       | iccl_ip_AXI;top     | step   |                          |                           |                    |              |            |          |             |                        |                           |

|       |                     | ImelM0 | Controller.              |                           |                    |              |            |          |             |                        |                           |

|       |                     | ^      |                          |                           |                    |              |            |          |             |                        |                           |

|       |                     |        | ImelMVector2.srefixVBase | sref                      | srefsKOption       |              |            |          |             |                        |                           |

|       |                     |        | tixlin                   | VecVWskdlcclStepState     | filfed;notit       |              |            |          |             |                        |                           |

|       |                     |        |                          | ImelMVectoritem2.sref     | Title              | Comment      |            |          |             |                        |                           |

|       |                     |        |                          | idle                      |                    |              |            |          |             |                        |                           |

|       |                     |        |                          | move                      |                    |              |            |          |             |                        |                           |

|       |                     |        |                          | ImelMVectoritem2.end      |                    |              |            |          |             |                        |                           |

|       |                     |        | ImelMVector2.end         |                           |                    |              |            |          |             |                        |                           |

|       |                     |        | ImelMCommand2.refNum     | sref                      | sreflxVRettype     | sreflvrRefWd | srefRvrRef | srefRerR | Comment     |                        |                           |

|       |                     |        |                          |                           |                    |              |            |          |             |                        |                           |

|       |                     |        | 0                        | moveto                    | void               |              |            |          |             |                        |                           |

|       |                     |        |                          | ImelAMCommandInvpar2.sref | sreflxWdbeVPartype | srefRefWdbe  | Length     | Defval   | srefRefWdbe | Comment                |                           |

|       |                     |        |                          | angle                     | uint16             |              |            | 0        |             | in stepper motor ste   | ps (4096 per rev.)        |

|       |                     |        |                          | Tstep                     | uint8              |              |            | 150      |             | in tkclk clocks: rps = | 10000 / (Tstep * 64 * 64) |

|       |                     |        |                          | ImelAMCommandInvpar2.end  |                    |              |            |          |             |                        |                           |

|       |                     |        |                          |                           |                    |              |            |          |             |                        |                           |

|       |                     |        | ImelMCommand2.end        |                           |                    |              |            |          |             |                        |                           |

|       |                     | ImelM0 | Controller.end           |                           |                    |              |            |          |             |                        |                           |

|       | ImelMModule.end     |        |                          |                           |                    |              |            |          |             |                        |                           |

| Imell | MUnit.end           |        |                          |                           |                    |              |            |          |             |                        |                           |

#### Overview | Composition | Example

|   | dbeFin v1.1.9                |                    |             |                   |                |                     |         |                             |        |       |     |       |   |

|---|------------------------------|--------------------|-------------|-------------------|----------------|---------------------|---------|-----------------------------|--------|-------|-----|-------|---|

|   | /Unit.sref                   |                    |             |                   |                |                     |         |                             |        |       |     |       | _ |

| I |                              |                    |             |                   |                |                     |         |                             |        |       |     |       |   |

|   | ImeIMModule.hsrefSup         | sref               |             |                   |                |                     |         |                             |        |       |     |       |   |

|   | iccl_ip_AXI;top              | step               |             |                   |                |                     |         |                             |        |       |     |       |   |

|   |                              |                    |             |                   |                |                     |         |                             |        |       |     |       |   |

|   |                              | ImeIMProcess.sref  | clkSrefWdbe | l asrSrefWdbeMS   | Falling        |                     | Extip   | Comment                     |        |       |     |       |   |

|   |                              | ор                 | mclk        | reset             | false          | state(init) or (sta | false   | main operation              |        |       |     |       |   |

|   |                              |                    | ImelMFsm.   |                   |                |                     |         |                             |        |       |     |       |   |

|   |                              |                    | ^           |                   |                |                     |         |                             |        |       |     |       |   |

|   |                              |                    |             | ImelMFsmstate     | sref           | Extip               | Comment |                             |        |       |     |       |   |

|   |                              |                    |             |                   | init           | false               |         |                             |        |       |     |       |   |

|   |                              |                    |             |                   | ImelAMFsm      | Cond1               | lp1     | Cond2                       | lp2    | Cond3 | lp3 | Cond4 |   |

|   |                              |                    |             |                   | inv            | regInvMoveto        | moveto  |                             |        |       |     |       |   |

|   |                              |                    |             |                   | inv            | regInvSet           | set     |                             |        |       |     |       |   |

|   |                              |                    |             |                   | inv            |                     | zero    |                             |        |       |     |       |   |

|   |                              |                    |             |                   | ready          | else                |         |                             |        |       |     |       |   |

|   |                              |                    |             |                   |                | stateStep.end       |         |                             |        |       |     |       | _ |

|   |                              |                    |             |                   |                | false               |         |                             |        |       |     |       |   |

|   |                              |                    |             |                   | ImelAMFsm      |                     | lp1     | Cond2                       | lp2    | Cond3 | lp3 | Cond4 |   |

|   |                              |                    |             |                   | runB           | Tstep/=0            |         | not targetNotSteady and rng | steady |       |     |       |   |

|   |                              |                    |             |                   | runB           | Tstep/=0            |         |                             |        |       |     |       | _ |

|   |                              |                    |             |                   |                | Tstep/=0            |         | else                        | hold   |       |     |       | _ |

|   |                              |                    |             |                   |                | stateStep.end       |         |                             | nord   |       |     |       | - |

|   |                              |                    |             |                   | intervent stra | Jucocopiena         |         |                             |        |       |     |       | - |

|   |                              |                    |             | <br>ImelMFsmstate | and            |                     |         |                             |        |       |     |       | _ |

|   |                              |                    | ImelMFsm.e  |                   | enu            |                     |         |                             |        |       |     |       |   |

|   |                              | ImeIMProcess.end   |             |                   |                |                     |         |                             |        |       |     |       |   |

|   | ImelMModule.end              | imeliviProcess.end |             |                   |                |                     |         |                             |        |       |     |       |   |

|   | ImelMModule.end<br>MUnit.end |                    |             |                   |                |                     |         |                             |        |       |     |       |   |

- Module definition, command definition, fine structure

- Linux side developer-facing: executable API method

#### Overview | Composition | Example

| <ul> <li>Module definit</li> <li>EXPLORER</li> <li>WSKD</li> <li>Indl</li> <li>Ins</li> <li>Ins</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>Linux side deve</li> <li>-mdl</li> <li>-rls</li> <li>-ezdevwskd</li> <li>-ymdi</li> <li>-rls</li> <li>-ezdevwskd</li> <li>-ymdi</li> <li>-rls</li> <li>-ezdevwskd</li> <li>-ymdi</li> <li>-ymdi</li> <li>-rls</li> <li>-ezdevwskd</li> <li>-ymdi</li> <li>-ymdi</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| <ul> <li>CurviskidicalCamacq.pp</li> <li>CurviskidicalCamacq.h</li> <li>CurviskidicalCamif.h</li> <li>CurviskidicalFaatdet.pp</li> <li>CurviskidicalFaatdet.pp</li> <li>CurviskidicalFaatdet.pp</li> <li>CurviskidicalFaatdet.pp</li> <li>CurviskidicalState.h</li> <li>CurviskidicalState.h</li> <li>CurviskidicalState.h</li> <li>CurviskidicalFaatdet.pp</li> <li>CurviskidicalState.h</li> <li>CurviskidicalState.h</li> <li>CurviskidicalState.pp</li> <li>CurviskidicalState.cpp</li> <li>CurviskidicalTkelksrc.pp</li> <li>CurviskidicalTkelksrc.pp</li> <li>CurviskidicalTkelksrc.h</li> <li>CurviskidicalTkelksrc.h</li> <li>CurviskidicalTkelksrc.h</li> <li>CurviskidicalTkelksrc.h</li> <li>CurviskidicalTkelksrc.h</li> <li>CurviskidicalState.h</li> <li>Static Decore::Cinds getWeckddSetInfo();</li> <li>Vuid getInfo(unta_t6 tixVState, untia_t Tstep);</li> <li>Static Decore::Cinds getWeckddSetInf;</li> <li>Vuid setCore::Cinds getWeckdSetInf;</li> <li>Vuid setCore::Cinds getWeckdSetInf;</li> <li>Vuid setCore::Cinds getWeckdSetInf;</li></ul> |  |

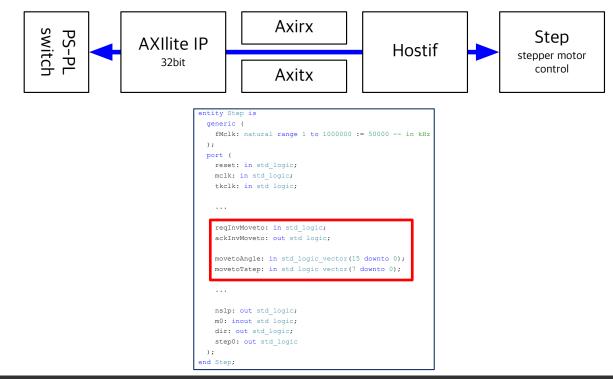

- Module definition, command definition, fine structure

- Linux side developer-facing: executable API method

- Linux side in background: translation into byte code and invocation of character device driver (AXI)

- FPGA side in background: reception and decoding of byte code in "host interface" module, CRC evaluation

- FPGA side developer-facing: handshake signals

EXPLORER WSKD > mdl > \_rls

v ezdevwskd

> UntWskdArty > UntWskdlccl > UntWskdMcep

> UntWskdUbdk C DevWskd.h C Wskd.cpp C Wskd.h

✓ fpgawskd > arty

✓ iccl > support Add v1 0.vhd

#### Overview | Composition | Example

- Module definition,

- Linux side develop •

- Linux side in backg ۰

- FPGA side in backg ۲ evaluation

- FPGA side develop ۲

|                        |         | Step.vhd — wskd                                                                                                          |

|------------------------|---------|--------------------------------------------------------------------------------------------------------------------------|

| PLORER                 |         | C CtrWskdlcclStep.h 2                                                                                                    |

| KD                     | A A O Ø | fpgawskd > iccl > ≣ Step.vhd                                                                                             |

| mdl                    |         | 1 file Step.vhd                                                                                                          |

| rls                    |         | <ol> <li> Step easy model controller implementation</li> <li> copyright: (C) 2016-2020 MPSI Technologies GmbH</li> </ol> |

| ezdevwskd              |         | 4 author: Catherine Johnson (auto-generation)                                                                            |

| UntWskdArty            |         | 5 date created: 1 Dec 2020<br>6 IP header ABOVE                                                                          |

| UntWskdlccl            |         | 6 IP header ABOVE<br>7                                                                                                   |

| UntWskdMcep            |         | 8 library ieee;                                                                                                          |

| UntWskdUbdk            |         | <pre>9 use ieee.std_logic_1164.all;<br/>10 use ieee.numeric_std.all;</pre>                                               |

| DevWskd.h              |         | 11                                                                                                                       |

|                        |         | 12 use work.Dbecore.all;<br>13 use work.Iccl.all;                                                                        |

| Wskd.cpp               |         | 13 use work.Iccl.all;<br>14                                                                                              |

| Wskd.h                 |         | 15 entity Step is                                                                                                        |

| fpgawskd               |         | 16 generic (<br>17 fMclk: natural range 1 to 1000000 := 50000 in kHz                                                     |

| arty                   |         | 18 );                                                                                                                    |

| iccl                   |         | 19 port (                                                                                                                |

| > support              |         | <pre>20 reset: in std_logic;<br/>21 mclk: in std_logic;</pre>                                                            |

| Add_v1_0.vhd           |         | 22 tkclk: in std_logic;                                                                                                  |

| Axirx_v2_0.vhd         |         | <pre>23 24 getInfoTixVState: out std logic vector(7 downto 0);</pre>                                                     |

| Axitx_v2_0.vhd         |         | 24 getInfoTixVState: out std_logic_vector(7 downto 0);<br>25 getInfoAngle: out std_logic_vector(15 downto 0);            |

| Bcdfreq_v1_0.vhd       |         | 26                                                                                                                       |

| Camacq.vhd             |         | 27 regInvMoveto: in std_logic;<br>28 ackInvMoveto: out std_logic;                                                        |

| Camif.vhd              |         | 29                                                                                                                       |

| Crc8005_32_v1_0.vhd    |         | <pre>30 movetoAngle: in std_logic_vector(15 downto 0);</pre>                                                             |

| Debounce_v1_0.vhd      |         | <pre>31 movetoTstep: in std_logic_vector(7 downto 0); 32</pre>                                                           |

| Featdet.vhd            |         | <pre>33 reqInvSet: in std_logic;</pre>                                                                                   |

| Hostif.vhd             |         | 34 ackInvSet: out std_logic;<br>35                                                                                       |

| I2c.vhd                |         | <pre>36 setRng: in std_logic_vector(7 downto 0);</pre>                                                                   |

|                        |         | <pre>37 setCcwNotCw: in std_logic_vector(7 downto 0);</pre>                                                              |

| Iccl_ip_v1_0_S_AXI.vhd |         | <pre>38 setTstep: in std_logic_vector(7 downto 0);<br/>39</pre>                                                          |

| E lccl.pdc             |         | <pre>40 reqInvZero: in std_logic;</pre>                                                                                  |

| E lccl.vhd             |         | <pre>41 ackInvZero: out std_logic; 42</pre>                                                                              |

| E Laser.vhd            |         | 43 step1: out std_logic;                                                                                                 |

| Mult_v1_0.vhd          |         | <pre>44 step2: out std_logic;</pre>                                                                                      |

| Rgbled4.vhd            |         | 45 step3: out std_logic;<br>46 step4: out std_logic;                                                                     |

| Rgbled5.vhd            |         | 47                                                                                                                       |

| Spimaster_v1_0.vhd     |         | <pre>48 stateOp_dbg: out std_logic_vector(7 downto 0) 49 ):</pre>                                                        |

| State.vhd              |         | 49 );<br>50 end Step;                                                                                                    |

| E Step.vhd             |         | 51                                                                                                                       |

| Sub_v1_0.vhd           |         | 52 architecture Step of Step is<br>53                                                                                    |

|                        |         | 22 I                                                                                                                     |

er device driver (AXI) ace" module, CRC

....

- Module definition, command definition, fine structure

- Linux side developer-facing: executable API method

- Linux side in background: translation into byte code and invocation of character device driver (AXI)

- FPGA side in background: reception and decoding of byte code in "host interface" module, CRC evaluation

- FPGA side developer-facing: handshake signals

- FPGA side left for manual implementation: finite state machine reacting to command invocation

EXPLORES

WSKD

> mdl

> \_rls

C Wskd.h

> artv

$\sim$  iccl

#### Overview | Composition | Example

- Module definition, c

- Linux side developer •

- Linux side in backgro ۰

- FPGA side in backgrd evaluation

- FPGA side developer

- FPGA side left for ma

Step.vhd - wskd C CtrWskdlcclStep.h 2 Step.vhd fpgawskd > iccl > ≡ Step.vhd 185 if regInvMoveto='1' then 186 -- IP impl.op.init.moveto --- IBEGIN 187 targetNotSteady := true; ezdevwskd 188 > UntWskdArty 189 -- determine shortest path 190 target := to integer(unsigned(movetoAngle)); > UntWskdlccl 191 dAngle := target - angle; > UntWskdMcen atTarget := (dAngle = 0); > UntWskdUbdk 194 C DevWskd.h if not atTarget them 195 196 if dAngle > 2048 then G Wskd.cpp 197 -- dAngle := dAngle - 4096; -- will become negative 198 ccwNotCw := true: 199 elsif dAngle < -2047 then fpgawskd 200 201 ccwNotCv := false: 202 elsif dAngle > 0 ther 203 ccwNotCw := false: > support 284 else Add\_v1\_0.vhd 205 cowNotCy := true: 206 end if; Axirx v2\_0.vhd 207 end if; Axitx v2 0.vhd 208 289 Tstep := to integer(unsigned(movetoTstep)); Bcdfreq\_v1\_0.vhd 210 Camacq.vhd ackInvMoveto sig <= '1': -- IP impl.op.init.moveto --- IEND Camif.vhd Crc8005\_32\_v1\_0.vhd stateOp <= stateOpInv:</pre> Debounce v1 0 vhd 216 elsif regInvSet='1' then-Featdet vhd 229 > elsif regInvZero='1' then-238 alse-Hostif vhd 248 end if; I2c.vhd 241 242 elsif stateOp=stateOpReady then lccl\_ip\_v1\_0\_S\_AXI.vhd 243 if Tstep/=0 ther Iccl.pdc 244 if not targetNotSteady and rng then 245 Iccl.vhd i := 0; -- IP impl.op.ready.steady --- ILINE 246 Laser.vhd 247 stateOp <= stateOpRunB</pre> Mult v1 0.vhd 248 249 elsif targetNotSteady and not atTarget then Rabled4.vhd 250 i := 0; --- IP impl.op.ready.target ---- ILINE 251 Rgbled5.vhd stateOn <= stateOnBunB Spimaster v1 0 vhd State.vhd 254 else -- IP impl.op.ready.hold --- IBEGIN Step.vhd 256 step1\_sig <= '0';</pre> Sub\_v1\_0.vhd step2 sig <= '0';</pre> 258 step3 sig <= '0'; Timeout\_v1\_0.vhd step4\_sig <= '0';</pre> Tkclksrc.vhd 260 -- IP impl.op.ready.hold --- IEND 261 Top.vhd 262 stateOp <= stateOpReady;</pre> end if 264 end if;

iracter device driver (AXI)

terface" module, CRC

#### o command invocation

Maintaining platform flexibility using a model-based software design approach

> mcep

meuwski

□ …

## Whiznium concepts

#### Modularity, transparency and re-usability

- Whiznium is Open Source; the generated code is subject to no license restrictions

- Whiznium generates well-organized, human-readable source code trees which can be synthesized / compiled "outof-the-box"

- Manual modifications are enabled through the concept of "insertion points"

- Upon source code iteration (e.g. following model extension) manual modifications are carried over to the next version

- Generated code relies on few, well-proven external libraries, all of which are Open Source. Standards are strictly followed

- WhizniumDBE features parametrized "module templates". Besides corresponding VHDL files, template-specific intervention in the WhizniumDBE master database through C++ code is possible

- WhizniumSBE features parametrized "capability templates". Also here, template-specific intervention in the WhizniumSBE master database through C++ code is possible

## Whiznium tools

#### Incorporation into existing developer workflows

- WhizniumSBE and WhizniumDBE are Linux-based "daemons" (and [fun fact] WhizniumSBE projects), which receive model information and send source code trees via HTTPS

- Java tools WhizniumDBE/SBE Bootstrap offer initialization of WhizniumDBE/SBE with project information stored in a local folder structure

- Java tools WhizniumDBE/SBE Iterator help transform local source code trees from the current version to the next. Here, API calls replace manual UI clicks

### Whiznium tools

#### Incorporation into existing developer workflows

| ٠ | WhizniumS     | • • WhizniumDBE Iterator                                                                           | daemons"       | • • • •                                  | WhizniumSBE Iterator                                     | , which receive |

|---|---------------|----------------------------------------------------------------------------------------------------|----------------|------------------------------------------|----------------------------------------------------------|-----------------|

|   | model infor   | Connect Disconnect                                                                                 | I HTTPS        | Connect                                  | Disconnect                                               |                 |

| • | Java tools V  | connected to 192.168.178.22:13105                                                                  | alization of ' |                                          | 2.168.178.22:13106                                       | ation stored in |

|   | a local folde | Projects<br>HelloWhiznium Device<br>Whiznium StarterKit Device                                     |                | Projects<br>HelloWhiznium<br>WhizniumDBE |                                                          |                 |

| ٠ | Java tools V  |                                                                                                    | rm local sou   | WhizniumSBE Eng<br>Whiznium License      |                                                          | on to the next. |

|   | Here, API ca  |                                                                                                    |                | WhizniumSBE<br>Whiznium Starter          | Kit                                                      |                 |

|   |               | current version is v1.0.2                                                                          |                | current version i                        | s v1.0.3                                                 |                 |

|   |               | Change project's current version                                                                   |                | Chang                                    | e project's current version                              |                 |

|   |               | Step version and iterate source code tree                                                          |                | Step ve                                  | rsion and iterate source code tree                       |                 |

|   |               | Iterate source code tree                                                                           |                | Iterat                                   | e source code tree                                       |                 |

|   |               | project selected                                                                                   |                | project selected                         |                                                          |                 |

|   |               | Successfully iterated source code tree of project Whiznium St<br>arterKit Device to version 1.0.2. |                | Successfully iter<br>arterKit to versio  | ated source code tree of project Whiznium St<br>n 1.0.3. |                 |

|   |               |                                                                                                    |                |                                          |                                                          |                 |

## Whiznium tools

#### Incorporation into existing developer workflows

- WhizniumSBE and WhizniumDBE are Linux-based "daemons" (and [fun fact] WhizniumSBE projects), which receive model information and send source code trees via HTTPS

- Java tools WhizniumDBE/SBE Bootstrap offer initialization of WhizniumDBE/SBE with project information stored in a local folder structure

- Java tools WhizniumDBE/SBE Iterator help transform local source code trees from the current version to the next. Here, API calls replace manual UI clicks

- WhizniumDBE code can be developed using the vendor-provided tools, e.g. Vivado, Quartus, Libero SoC or Simplicity Studio

- WhizniumSBE code can be (cross-)compiled using the industry-standard tool chains gcc/Clang. (Remote-)Debugging can be done using e.g. VS Code

- The Yocto project helps building custom Embedded Linux distributions for each FPGA-SoC platform. WhizniumSBE projects run on those distributions

### Whiznium resources

• Both Whiznium tools are available free of charge on GitHub, including installation instructions

https://github.com/mpsitech/The-Whiznium-Documentation

- The Open Source StarterKit ist available for various hardware platforms, with vendor-specific instructions also available on <u>GitHub</u>

- "The Whiznium Developer Experience" on YouTube is an ongoing Webinar series on Whiznium

- For advanced users WhizniumSBE/DBE cheat sheets are available which serve as reference for writing model files

WhizniumDBE Cheat Sheet Matter The Durice Builder's Edition

Maintaining platform flexibility using a model-based software design approach

FPGA Conference Europe 2022

#### Conclusion

- Avoid vendor lock-in where possible

- Limit use of block diagrams

- Use generic code for simple things (UART / SPI / AXIlite, math)

- Write wrappers around vendor-specific silicon (memory / high-speed transceivers)

- Model-based source code generation helps further

- Can abstract away hardware at the crucial host-FPGA interconnect, "single source of truth" maintains host-FPGA integrity

- WhizniumDBE comes with a set of above mentioned wrappers

- WhizniumDBE maintains a coarse-to-fine project model in a database and is user-extensible (by means of C++ code, e.g. for frequently used IP)

### Thank You! Questions?

#### Also, feel free to connect.

- <u>https://www.linkedin.com/in/wirthmua</u>

- <u>https://github.com/mpsitech</u>

Alexander Wirthmüller Founder & Director

Phone: +49 (89) 4524 3826 Mobile: +49 (175) 918 5480 E-Mail: aw@mpsitech.com

MPSI Technologies GmbH Agnes-Pockels-Bogen 1 80992 Munich Germany www.mpsitech.com