# A MODEL-BASED APPROACH TO MASTERING COMPLEXITY IN FPGA-SoC SOFTWARE DEVELOPMENT

Alexander Wirthmüller aw@mpsitechnologies.com

## Introduction Me and MPSI Technologies

- Diploma in Electrical Engineering

- Based in Munich

- R&D Engineer at Mynaric (FPGA-based error-correction algorithms for free-space optical laser communications)

- Founder and Director at MPSI Technologies

- MPSI Technologies: make Embedded Software development more fun by replacing repetitive tasks by model-based source code generation

## **FPGA-SoC** landscape

#### Devices and applications

#### **Product lines**

#### Selection discussed here: CPU complex can run Embedded Linux

## AMDA ZYNQ.

- from 2011: Zynq 7000 with Dual 32-bit ARM CPU and SRAMbased FPGA, internally connected via AXI

- from 2016: Zynq UltraScale+ with Quad 64-bit ARM CPU and additional real-time cores / accelerators

- from 2012: CycloneV with Dual 32-bit ARM CPU

- from 2016: Stratix 10 with Quad 64-bit ARM CPU

• from 2019: PolarFire SoC with Quad 64-bit RISC-V CPU and antifuse-based FPGA

#### Typical applications

- classical FPGA applications where additional high-level control is of advantage

- "data reduction" or pre-processing of highbandwidth sources

- cameras: binning, pixel-level filters, compression, feature and object detection

- ADC's: spectral analysis, DSP filters

- clock-precise signaling for mixed-signal ASIC's

- not considered here: data center and hardware acceleration applications

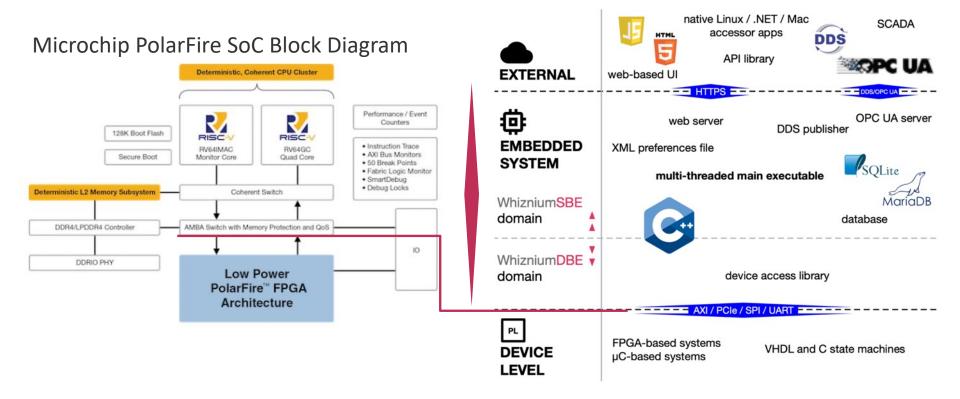

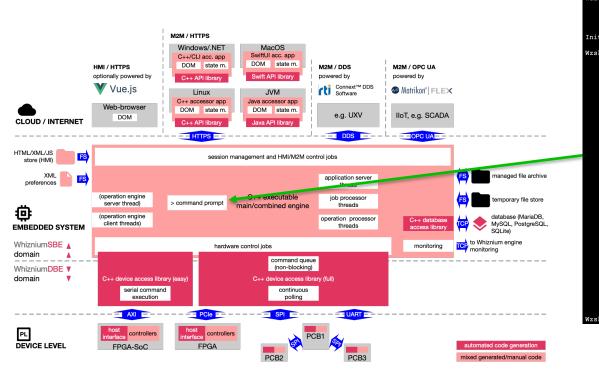

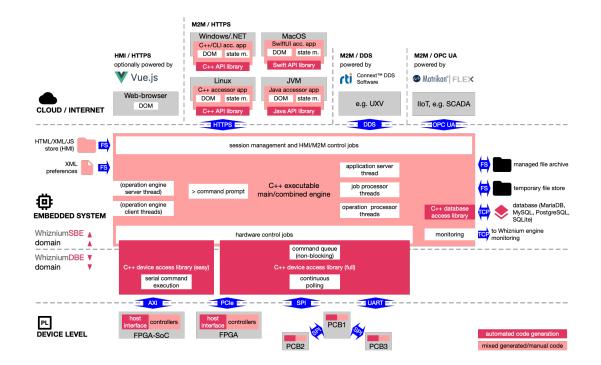

## The FPGA-SoC software full stack From VHDL to C++ to HTTPS and XML

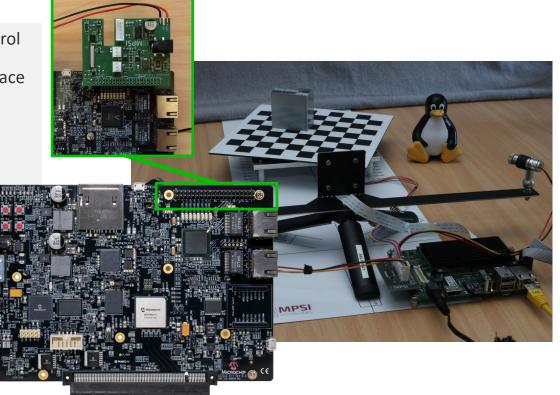

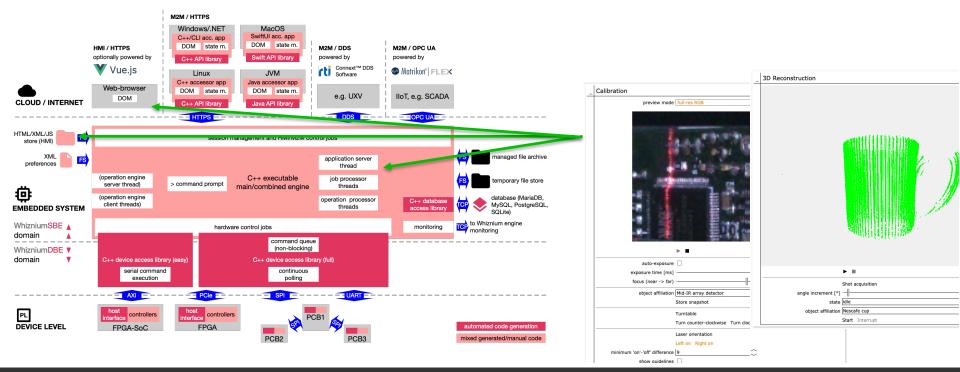

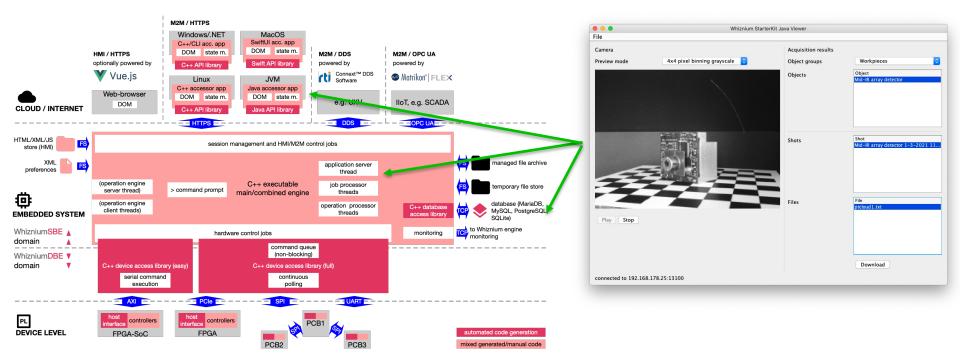

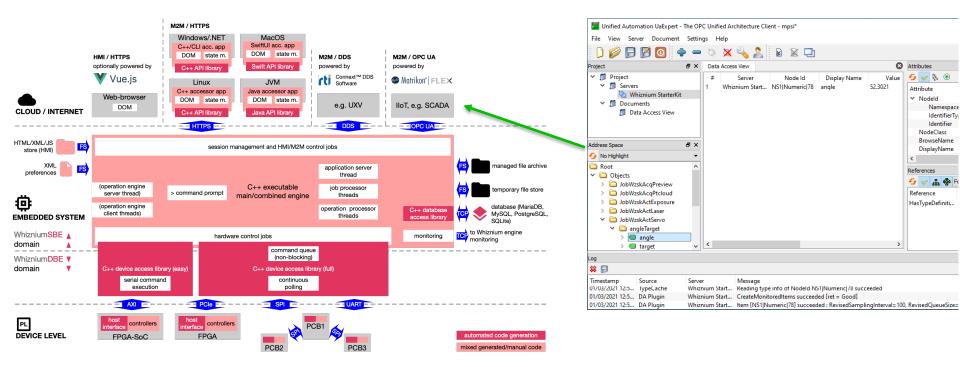

## Demo project: hardware Tabletop 3D laser scanner

- turntable with with stepper motor control

- 5 megapixel camera with MIPI CSI interface

- two intensity-modulated line lasers

- Microchip PolarFire SoC Icicle kit with adapter PCB

#### From camera raw data to point cloud display in web browser

#### From camera raw data to point cloud display in web browser

A Model-based Approach to Mastering Complexity in FPGA-SoC Software Development

embedded world Conference 2022

#### From camera raw data to point cloud display in web browser

#### From camera raw data to point cloud display in web browser

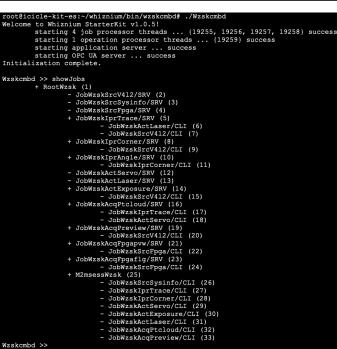

## Embedded software model description

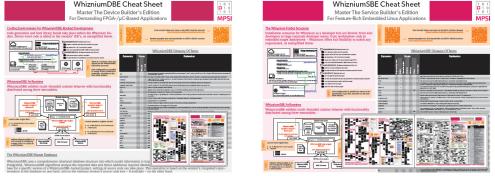

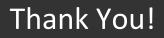

#### WhizniumDBE for FPGA layer, WhizniumSBE for Linux application software

- successive model composition within an SQL database using import (I) and generation (G) steps

- output of source code trees only thereafter

- text-based model files ("diffable")

#### WhizniumDBE (Device Builder's Edition)

- Modular structure (I)

- Command set and buffer transfers (I)

- Data flows and algorithms (I)

- Fine structure (G)

- Custom fine structure (I)

- Finalization (G)

#### WhizniumSBE (Service Builder's Edition)

- Deployment information (I)

- Global features (I)

- Database structure (I)

- Basic user interface structure (I)

- Import/export structure (I)

- Operation pack structure (I)

- Custom jobs (I)

- User interface (G)

- Custom user interface features (I)

- Job tree (G)

- Custom job tree features (I)

- Finalization (G)

• module definition, command definition, fine structure

| lexWdbeMo            | ll v1.1.14            |                 |                                    |             |             |                |               |        |

|----------------------|-----------------------|-----------------|------------------------------------|-------------|-------------|----------------|---------------|--------|

| melMUnit             | srefSilRefWdbeMUnit   | sref            | Title                              | Easy        | srefKToolch | Comment        |               |        |

| fpga                 | mpfs250t-fcvg484      | iccl            | Microchip PolarFire Soc Icicle kit | true        | libero      |                |               |        |

|                      | ImelMModule.sreflxVBa | hsrefSupRefWdl  | srefTplRefWdbeMModule              | sref        | Comment     |                |               |        |

|                      | wrp                   |                 | mpfs_ip_AXI_v1_0                   | iccl_ip_AXI |             |                |               |        |

|                      | top                   | iccl_ip_AXI     | top_mchp_v1_0                      | top         |             |                |               |        |

|                      |                       | ImelAMModule    | Val                                |             |             |                |               |        |

|                      |                       | fExtclk         | 125000                             |             |             |                |               |        |

|                      |                       | extresetNNotP   | true                               |             |             |                |               |        |

|                      | ImelAMMod             |                 | Par.end                            |             |             |                |               |        |

|                      |                       | ImelMGeneric.s  | Defval                             |             |             |                |               |        |

|                      |                       | fMclk           | 50000                              |             |             |                |               |        |

|                      |                       | ImelMGeneric.e  | nd                                 |             |             |                |               |        |

|                      |                       |                 |                                    |             |             |                |               |        |

| ectr iccl_ip_AXI;top |                       | iccl_ip_AXI;top |                                    | step        | stepper mot | or control (28 | BYJ-48 via Ul | N2003) |

|                      |                       |                 |                                    |             |             |                |               |        |

|                      | ImelMModule.end       |                 |                                    |             |             |                |               |        |

| melMUnit.            | end                   |                 |                                    |             |             |                |               |        |

| lexW  | dbeCsx v1.1.9       |                     |                          |                           |                    |              |           |            |             |                        |                           |

|-------|---------------------|---------------------|--------------------------|---------------------------|--------------------|--------------|-----------|------------|-------------|------------------------|---------------------------|

| Imell | MUnit.sref          |                     |                          |                           |                    |              |           |            |             |                        |                           |

| iccl  |                     |                     |                          |                           |                    |              |           |            |             |                        |                           |

|       | ImeIMModule.hsrefSu | ip sref             |                          |                           |                    |              |           |            |             |                        |                           |

|       | iccl_ip_AXI;top     | step                |                          |                           |                    |              |           |            |             |                        |                           |

|       |                     | ImelM               | Controller.              |                           |                    |              |           |            |             |                        |                           |

|       |                     | ^                   |                          |                           |                    |              |           |            |             |                        |                           |

|       |                     |                     | ImelMVector2.sreflxVBase | sref                      | srefsKOption       |              |           |            |             |                        |                           |

|       |                     |                     | tixlin                   | VecVWskdlcclStepState     | filfed;notit       |              |           |            |             |                        |                           |

|       |                     |                     |                          | ImelMVectoritem2.sref     | Title              | Comment      |           |            |             |                        |                           |

|       |                     |                     |                          | idle                      |                    |              |           |            |             |                        |                           |

|       |                     |                     |                          | move                      |                    |              |           |            |             |                        |                           |

|       |                     |                     |                          | ImelMVectoritem2.end      |                    |              |           |            |             |                        |                           |

|       |                     |                     | ImelMVector2.end         |                           |                    |              |           |            |             |                        |                           |

|       |                     |                     | ImeIMCommand2.refNum     | sref                      | sreflxVRettype     | sreflvrRefWd | srefRvrRe | f srefRerR | Comment     |                        |                           |

|       |                     |                     |                          |                           |                    |              |           |            |             |                        |                           |

|       |                     |                     | 0                        | moveto                    | void               |              |           |            |             |                        |                           |

|       |                     |                     |                          | ImelAMCommandInvpar2.sref | sreflxWdbeVPartype | srefRefWdbe  | Length    | Defval     | srefRefWdbe | Comment                |                           |

|       |                     |                     |                          | angle                     | uint16             |              |           | 0          |             | in stepper motor ste   | eps (4096 per rev.)       |

|       |                     |                     |                          | Tstep                     | uint8              |              |           | 150        |             | in tkclk clocks: rps = | 10000 / (Tstep * 64 * 64) |

|       |                     |                     |                          | ImelAMCommandInvpar2.end  |                    |              |           |            |             |                        |                           |

|       |                     |                     |                          |                           |                    |              |           |            |             |                        |                           |

|       |                     |                     | ImeIMCommand2.end        |                           |                    |              |           |            |             |                        |                           |

|       |                     | ImeIMController.end |                          |                           |                    |              |           |            |             |                        |                           |

|       | ImeIMModule.end     |                     |                          |                           |                    |              |           |            |             |                        |                           |

| Imell | MUnit.end           |                     |                          |                           |                    |              |           |            |             |                        |                           |

## Deep dive I: from C++ command to RTL finite state machine

#### Control of turntable stepper motor

| lexWo | beFin v1.1.9         |                   |             |               |           |                     |         |                                  |        |       |     |       |     |

|-------|----------------------|-------------------|-------------|---------------|-----------|---------------------|---------|----------------------------------|--------|-------|-----|-------|-----|

| ImelN | 1Unit.sref           |                   |             |               |           |                     |         |                                  |        |       |     |       |     |

| iccl  |                      |                   |             |               |           |                     |         |                                  |        |       |     |       |     |

|       | ImeIMModule.hsrefSup | sref              |             |               |           |                     |         |                                  |        |       |     |       |     |

|       | iccl_ip_AXI;top      | step              |             |               |           |                     |         |                                  |        |       |     |       |     |

|       |                      |                   |             |               |           |                     |         |                                  |        |       |     |       |     |

|       |                      | ImeIMProcess.sref | clkSrefWdbe | asrSrefWdbeMS | Falling   | Syncrst             | Extip   | Comment                          |        |       |     |       |     |

|       |                      | ор                | mclk        | reset         | false     | state(init) or (sta | false   | main operation                   |        |       |     |       |     |

|       |                      |                   | ImeIMFsm.   |               |           |                     |         |                                  |        |       |     |       |     |

|       |                      |                   | ^           |               |           |                     |         |                                  |        |       |     |       |     |

|       |                      |                   |             | ImeIMFsmstate | sref      | Extip               | Comment |                                  |        |       |     |       |     |

|       |                      |                   |             | 0             | init      | false               |         |                                  |        |       |     |       |     |

|       |                      |                   |             |               | ImelAMFsm | Cond1               | lp1     | Cond2                            | lp2    | Cond3 | lp3 | Cond4 | lp4 |

|       |                      |                   |             |               | inv       | reqInvMoveto        | moveto  |                                  |        |       |     |       |     |

|       |                      |                   |             |               | inv       | reqInvSet           | set     |                                  |        |       |     |       |     |

|       |                      |                   |             |               | inv       | reqInvZero          | zero    |                                  |        |       |     |       |     |

|       |                      |                   |             |               | ready     | else                |         |                                  |        |       |     |       |     |

|       |                      |                   |             |               | ImelAMFsm | stateStep.end       |         |                                  |        |       |     |       |     |

|       |                      |                   |             | 0             | ready     | false               |         |                                  |        |       |     |       |     |

|       |                      |                   |             |               | ImelAMFsm | Cond1               | lp1     | Cond2                            | lp2    | Cond3 | lp3 | Cond4 | lp4 |

|       |                      |                   |             |               | runB      | Tstep/=0            |         | not targetNotSteady and rng      | steady |       |     |       |     |

|       |                      |                   |             |               | runB      | Tstep/=0            |         | targetNotSteady and not atTarget | target |       |     |       |     |

|       |                      |                   |             |               | ready     | Tstep/=0            |         | else                             | hold   |       |     |       |     |

|       |                      |                   |             |               | ImelAMFsm | stateStep.end       |         |                                  |        |       |     |       |     |

|       |                      |                   |             |               |           |                     |         |                                  |        |       |     |       |     |

|       |                      |                   |             | ImeIMFsmstate | .end      |                     |         |                                  |        |       |     |       |     |

|       |                      |                   | ImelMFsm.e  | nd            |           |                     |         |                                  |        |       |     |       |     |

|       |                      | ImeIMProcess.end  |             |               |           |                     |         |                                  |        |       |     |       |     |

|       | ImelMModule.end      |                   |             |               |           |                     |         |                                  |        |       |     |       |     |

| ImelN | 1Unit.end            |                   |             |               |           |                     |         |                                  |        |       |     |       |     |

- module definition, command definition, fine structure

- Linux side developer-facing: executable API method

CtrWskdlcclStep.h - wskd module definit 🗳 EXPLORER C CtrWskdlcclStep.h 2 • Ш … WSKD C C V Ø ezdevwskd > UntWskdlccl > C CtrWskdlcclStep.h > 4 CtrWskdlcclStep /\*\* > \_mdl \* \file CtrWskdIcclStep.h Linux side deve > \_rls 3 \* step controller (declarations) \* \copyright (C) 2016-2020 MPSI Technologies GmbH v ezdevwskd \* \author Alexander Wirthmueller (auto-generation) > UntWskdArty \* \date created: 23 Oct 2021 VuntWskdlccl \*/ 8 // IP header --- ABOVE CtrWskdlcclCamacq.cpp C CtrWskdlcclCamacq.h 10 #ifndef CTRWSKDICCLSTEP\_H 11 #define CTRWSKDICCLSTEP\_H G CtrWskdIcclCamif.cpp 12 C CtrWskdlcclCamif.h 13 #include "Wskd.h" 14 CtrWskdlcclFeatdet.cpp 15 #define CmdWskdIcclStepGetInfo CtrWskdIcclStep::CmdGetInfo C CtrWskdlcclFeatdet.h 16 17 #define VecVWskdIcclStepCommand CtrWskdIcclStep::VecVCommand CtrWskdlcclLaser.cpp 18 #define VecVWskdIcclStepState CtrWskdIcclStep::VecVState C CtrWskdlcclLaser.h 19 20 /\*\* CtrWskdlcclState.cpp 21 \* CtrWskdIcclStep C CtrWskdlcclState.h 22 \*/ 23 class CtrWskdIcclStep : public CtrWskd { CtrWskdlcclStep.cpp 24 C CtrWskdlcclStep.h 25 // ... 26 G CtrWskdlcclTkclksrc.cpp 27 public: C CtrWskdlcclTkclksrc.h 28 // ... 29 G UntWskdlccl\_vecs.cpp 30 static Dbecore::Cmd\* getNewCmdGetInfo(); C UntWskdlccl\_vecs.h 31 void getInfo(uint8\_t& tixVState, uint16\_t& angle); C UntWskdlccl.cpp 32 33 static Dbecore::Cmd\* getNewCmdMoveto(); C UntWskdlccl.h 34 void moveto(const uint16 t angle, const uint8 t Tstep); 35 > UntWskdMcep 36 static Dbecore::Cmd\* getNewCmdSet(); > UntWskdUbdk 37 void set(const bool rng, const bool ccwNotCw, const uint8\_t Tstep); C DevWskd.h 38 39 static Dbecore::Cmd\* getNewCmdZero(); G Wskd.cpp 40 void zero(); C Wskd.h 41 42 }; > fpgawskd 43 > mcuwskd 44 #endif

- module definition, command definition, fine structure

- Linux side developer-facing: executable API method

- Linux side in background: translation into byte code and invocation of character device driver (AXI)

- FPGA side in background: reception and decoding of byte code in "host interface" module, CRC evaluation

- FPGA side developer-facing: handshake signals

- module definition,

- Linux side develop

- Linux side in backg

- FPGA side in backg evaluation

- FPGA side develop

| ad     24     getInfoTixVState: out std_logic/vector(7 downto 0);       byhd     26       byhd     26       yrl_Ovhd     27       ackInvNoveto: out std_logic;       advid     28       yrl_Ovhd     30       ackInvNoveto: out std_logic;       33     reqInvSet: in std_logic;       34     ackInvSet: out std_logic;       35     setTstep: in std_logic/vector(7 downto 0);       36     setTstep: in std_logic/vector(7 downto 0);       37     setTstep: in std_logic/vector(7 downto 0);       38     setTstep: in std_logic/vector(7 downto 0);       39     reqInvSet: in std_logic/vector(7 downto 0);       31     ackInvSet: out std_logic;       32     setTstep: in std_logic/vector(7 downto 0);       33     setTstep: in std_logic/vector(7 downto 0);       34     ackInvSet: out std_logic;       35     setTstep: in std_logic/vector(7 downto 0);       36     setTstep: in std_logic;       37     setTstep: in std_logic;       38     setTstep: in std_logic;       39     reqInvZero: in std_logic;       43     step1: out std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |           | Step.vhd — wskd                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-------------------------------------------------------------------------------------------------------|

| <pre>1 - file Step.vhd<br/>2 - file Step.vhd<br/>3 - copyright: (C) 2016-2020 MPSI Technologies Gabi<br/>4 - author: Catherine Johnson (auto-generation)<br/>5 - date created: 1 Dec 2020<br/>6 - IP header A0002<br/>1 Ubrary isee;<br/>9 use isee.std.logic,1164.01;<br/>10 use work.Decore.all;<br/>10 use work.Decore.all;<br/>11 use work.Decore.all;<br/>12 use work.Decore.all;<br/>13 use work.Decore.all;<br/>14 use work.Decore.all;<br/>15 entity Step is<br/>16 port (<br/>17 fft(k: natural range 1 to 1000000 := 50000 in kHz<br/>17 j;<br/>16 port (<br/>17 fft(k: natural range 1 to 1000000 := 50000 in kHz<br/>18 j;<br/>19 port (<br/>10 fft(k: natural range 1 to 1000000 := 50000 in kHz<br/>19 port (<br/>10 fft(k: natural range 1 to 1000000 := 50000 in kHz<br/>10 j;<br/>10 port (<br/>10 fft(k: natural range 1 to 1000000 := 50000 in kHz<br/>10 j;<br/>10 port (<br/>11 fft(k: natural range 1 to 1000000 := 50000 in kHz<br/>12 ttclk: in std_logic;<br/>13 ectinofworts: in std_logic;<br/>14 ectin std_logic;<br/>15 eftingi: in std_logic;<br/>16 extInvMoveto: un std_logic;<br/>17 entity Step: in std_logic;<br/>18 extInvMoveto: in std_logic;<br/>19 movetoTatep: in std_logic;<br/>10 extInvMoveto: in std_logic;<br/>10 extInvMoveto: in std_logic;<br/>10 extInvMoveto: in std_logic;<br/>10 extInvMoveto: in std_logic;<br/>10 extInvSter: in std_logic;<br/>11 extInvSter: in std_logic;<br/>12 extInvSter: in std_logic;<br/>13 extInvSter: in std_logic;<br/>14 extInvSter: in std_logic;<br/>15 extInvSter: in std_logic;<br/>16 step3: out std_logic;<br/>17 extInvSter: in std_logic;<br/>18 extInvSter: in std_logic;<br/>19 extInvSter: in std_logic;<br/>10 extInvSter: in std_logic;</pre> |           |           | C CtrWskdlcclStep.h 2                                                                                 |

| <pre>4 author: (atherine Johnson (auto-generation) 5 date created: l Dec 2020 6 IP header ABOVE 7 Use work.Decore.all; 10 use ieee.numeric_std.all; 11 use work.Decore.all; 12 use work.Decore.all; 13 use work.Decore.all; 14 entity Step is 15 entity Step is 16 entity Step is 16 entity Step is 17 entity Step is 18 entity Step is 19 entity Step is 19 entity Step is 19 entity Step is 10 entity Ste</pre>                                                                                                                                                                                                         |           | B, B, V ₽ | 1 file Step.vhd<br>2 Step easy model controller implementation                                        |

| <pre>     ibrary ieee;     we ieee.numeric_std.all;     we we ieee.numeric_std.all;     we work.Decore.all;     we work.Decore.all;     we work.Iccl.all;     entity Step is     pertit (         fmcki: natural range 1 to 1000000 := 50000 in kHz     };     fmcki: natural range 1 to 1000000 := 50000 in kHz     };     molk: in std_logic;     molk: in std_logic;     ackInvise: out std_logic,vector(7 downto 0);     regInvKoveto: out std_logic;     ackInvise: in std_logic;     std[logic;     ackInvise: in std_logic;     std[logic;     std[log</pre>                                                                                                                                                                                                  |           | •         | <ul> <li>4 author: Catherine Johnson (auto-generation)</li> <li>5 date created: 1 Dec 2020</li> </ul> |

| B         library ices;           9         use ices.tul_opic_l164.all;           10         use ices.tul_opic_l164.all;           11         use work.Decore.all;           12         use work.Decore.all;           13         use work.Decore.all;           14         entity Step is           15         entity Step is           16         peeric (           17         'Mtk: natural range 1 to 100000 := 50000 in kHz           18         2           19         port (           10         rest: in std_lopic;           11         use work.listic.out std_lopic_vector(7 downto 0);           11         getInfoixVState: out std_lopic_vector(13 downto 0);           11         movetoAngle: in std_lopic_vector(13 downto 0);           12         reqInvMoveto: in std_lopic;           13         movetoState; in std_lopic;           14         3           15         setFiste; in std_lopic;           16         3           16         3           17         reqInvSet: in std_lopic;           18         setFiste; in std_lopic;           19         reqInvSet: in std_lopic;           10.vhd         3           10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |           |                                                                                                       |

| O         use isee.std_logic_1164.01;           is         0         use isee.numeric_std.01;           is         0         use work.Bcc.er.01;           is         0         use work.Iccl.01;           is         0         entity Step is           generic (         0         mCk: natural range 1 to 1000000 := 50000 — in kHz           is         0         port (           is         0         getInfoTixVState: out std_logic; vector(7 downto 0);           id         22         tkckk: in std_logic;           id         23         getInfoTixVState: out std_logic; vector(7 downto 0);           id         24         getInfoTixVState: out std_logic; vector(15 downto 0);           id         25         regInvNoveto: out std_logic;           id         26         regInvNoveto: out std_logic;           id         26         regInvNoveto: out std_logic;           id         30         movetOnTite; in std_logic;           id         11         getInfoRingVector(15 downto 0);           id         12         regInvZero: in std_logic;           id         13         movetOnTite; in std_logic;           id         14         istep: out std_logic;           id         setTstap: in st                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |           |                                                                                                       |

| <pre>1</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0         |           |                                                                                                       |

| 12     use work.Dbccore.all;       13     use work.Dcclall;       14     entity Step is       15     entity Step is       16     pencic (       17     / McK: natural range 1 to 1000000 := 50000 in kHz       18     21       19     port (       14     22       15     ecti: in std_logic;       16     22       17     / McK: in std_logic, vector(7 downto 0);       28     getInfoIxWState: out std_logic_vector(7 downto 0);       29     reqInMoveto: in std_logic, vector(15 downto 0);       20     reqInMoveto: out std_logic;       21     reqInMoveto: out std_logic;       22     reqInMoveto: out std_logic;       23     reqInvSet: in std_logic;       24     setFiste: in std_logic;       25     setFiste: in std_logic;       26     setFiste: in std_logic;       27     reqInvSet: in std_logic;       28     setFiste: in std_logic;       29     reqInvSet: in std_logic;       30     reqInvZero: in std_logic;       31     setFiste: in std_logic;       32     reqInvZero: in std_logic;       33     reqInvZero: in std_logic;       34     stepI: out std_logic;       35     stepI: out std_logic; <td< td=""><td>c .</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | c .       |           |                                                                                                       |

| iiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |           |                                                                                                       |

| id       entity Step is         id       generic (         if       (%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |           |                                                                                                       |

| 16       generic i         17       MCLK: anzural range 1 to 1000000 := 50000 in kHz         18       );         19       port (         12       reset: in std_logic;         14       22         15       reset: in std_logic;         16       22         17       relnfv5ixVState: out std_logic; vector(7 downto 0);         18       23         19       getInfoIxVState: out std_logic; vector(15 downto 0);         10       25         10       26         10       27         10       28         10       28         11       movetoAngle: in std_logic; vector(15 downto 0);         28       movetoStage: in std_logic;         29       movetoStage: in std_logic;         20.Vhd       33         23       reqInvSet: in std_logic;         34       ackInvSet: in std_logic;         35       setTste: in std_logic;         36       setTste: in std_logic;         37       setCowlot: in std_logic;         38       setTste: in std_logic;         39       reqInvZero: unt std_logic;         39       reqInvZero: unt std_logic;         34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |           |                                                                                                       |

| 1 <pre>             f Mt(k: natural range 1 to 1000000 := 50000 in kHz             in kHz             if                   port (</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |           |                                                                                                       |

| 18     );       19     port (       19     port (       20     rest: in std_logic;       21     mclk: in std_logic;       22     tkclk: in std_logic;       23     getInfoIxWState: out std_logic;       24     getInfoIxWState: out std_logic;       25     getInfoIxWState: out std_logic;       26     getInfoIxWState: out std_logic;       27     realnMveto: out std_logic;       28     movetOAngle: in std_logic;       29     movetOAngle: in std_logic;       20     movetOAngle: in std_logic;       33     reqInvSet: in std_logic;       34     setFing: in std_logic;       35     setFing: in std_logic;       36     setFing: in std_logic;       37     setCaNetCu: in std_logic;       38     setFing: in std_logic;       39     reqInvZero: unt std_logic;       41     ackInvZero: unt std_logic;       42     stepI: out std_logic;       43     stepI: out std_logic;       44     stepI: out std_logic;       45     stepB: out std_logic;       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |           |                                                                                                       |

| ind     ind                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |           |                                                                                                       |

| 20 <pre>regin: in std_logi;<br/>mclk: in std_logi;<br/>22         1d       23         21       mclk: in std_logi;<br/>22         1d       24         24       getInfoIxWState: out std_logi; vector(7 downto 0);<br/>34         1d       25         1d       26         1d       27         1d       28         1d       26         1d       27         1d       28         1d       38         1d       39         1d       34         25_AXLvhd       35         25_AXLvhd       36         26       setFing: in std_logic/vector(7 downto 0);         37       setCawlotk: in std_logic;         38       setFing: in std_logic;         39       reqInvZero: in std</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |           |                                                                                                       |

| i         22         tkclk: in std_logic;           id         23         getInfoTixVState: out std_logic,vector(7 downto 0);           id         25         getInfoAngle: out std_logic,vector(15 downto 0);           ivvid         26         reqInVMoveto: in std_logic;           ivvid         28         ackInvMoveto: out std_logic;           ivvid         28         ackInvMoveto: out std_logic;           ivvid         38         movetoTstep: in std_logic,vector(7 downto 0);           ivvid         38         reqInvSers: in std_logic,vector(7 downto 0);           ivvid         38         setEng: in std_logic;           ivvid         39         reqInvZero: in std_logic;           ivvid         ivvid_logic;         ststd_logic;           ivvid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |           |                                                                                                       |

| dd     24     getInfoTixVState: out std_logic_vector(7 downto 0);       ydd     25     getInfoTixVState: out std_logic_vector(15 downto 0);       ylowhd     26     reqInvNoveto: in std_logic;       ackInvNoveto: out std_logic;     ackInvNoveto: out std_logic;       yl_Ovhd     30     movetOAngle: in std_logic;       32     reqInvSet: in std_logic;       33     reqInvSet: in std_logic;       34     ackInvSet: out std_logic;       35     setTeng: in std_logic,vector(7 downto 0);       36     setTeng: in std_logic,vector(7 downto 0);       37     setTeng: in std_logic,vector(7 downto 0);       38     setTstep: in std_logic;       39     reqInvZero: in std_logic;       40     44       41     ackInvZero: out std_logic;       42     step1: out std_logic;       43     step2: out std_logic;       44     step2: out std_logic;       45     step3: out std_logic;       46     step3: out std_logic;       47     stateOp_d0g: out std_logic;       48     step3: out std_logic;       49     j;       50     end Step;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |           | <pre>21 mclk: in std_logic;</pre>                                                                     |

| Main     24     getInfoInVState: out std_logic_vector(7 downto 0);<br>getInfoAngle: out std_logic;<br>ackInvMoveto: out std_logic;<br>ackInvMoveto: out std_logic;<br>ackInvMoveto: out std_logic;<br>ackInvMoveto: out std_logic;<br>ackInvSter: in std_logic_vector(7 downto 0);<br>ackInvSter: in std_logic;<br>ackInvSter: in std_logic/vector(7 downto 0);<br>setSAXLvhd       S_AXLvhd     36       setInvZero: in std_logic;<br>ackInvZero: out std_logic;<br>ackInvZero: in std_logic;<br>ackInvZero: out std_logic;                                                                                  | 1         |           |                                                                                                       |

| dd     25     getInfoAngle: out std_logic_vector(15 downto 0);       b,vhd     27     reqInvBoveto: in std_logic;       28     ackInvMoveto: out std_logic;       29     movetoAngle: in std_logic;       30     movetoAngle: in std_logic,vector(15 downto 0);       20.vhd     31       31     movetoAngle: in std_logic,vector(7 downto 0);       32     reqInvSet: in std_logic,vector(7 downto 0);       33     reqInvSet: in std_logic,vector(7 downto 0);       34     ackInvSet: out std_logic,vector(7 downto 0);       35     setTstep: in std_logic,vector(7 downto 0);       36     setTstep: in std_logic;       37     setCoNot(x: in std_logic;       38     setTstep: in std_logic;       39     reqInvZero: in std_logic;       40     45       41     ackInvZero: out std_logic;       42     stetPi: out std_logic;       43     stetPi: out std_logic;       44     stepPi: out std_logic;       45     stetPi: out std_logic;       46     stetPi: out std_logic;       47     stateOp_dog: out std_logic;       48     stateOp_dog: out std_logic;       49     ;       50     end Step;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nd        |           |                                                                                                       |

| Avhd     26     reqInvMoveto: in std_logic;       28     ackInvMoveto: out std_logic;       28     ackInvMoveto: out std_logic;       29     movetAngle: in std_logic_vector(15 downto 0);       20vhd     30     movetAngle: in std_logic_vector(7 downto 0);       20vhd     32     reqInvSerie in std_logic;       34     ackInvSet: out std_logic;     ackInvSet: out std_logic;       35     setRmg: in std_logic_vector(7 downto 0);     setStep: in std_logic;       36     setRmg: in std_logic_vector(7 downto 0);     setStep: in std_logic;       37     setCoNotCv: in std_logic;     setStep: in std_logic;       40     43     step1: out std_logic;       41     ackInvZero: out std_logic;       42     step1: out std_logic;       43     step1: out std_logic;       44     statelogic;       45     step3: out std_logic;       46     statelogic;       47     statelogic;       48     statelogic;       49     j;       50     architecture Step of Step is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nd        |           |                                                                                                       |

| 27       reqInv6veto: in std_logic;<br>ackInv6veto: out std_logic;<br>ackInv6veto: out std_logic;<br>all movetAngle: in std_logic,vector(15 downto 0);<br>all movetoTstep: in std_logic,vector(7 downto 0);<br>all movetoTstep: in std_logic;<br>ackInvSet: out std_logic;<br>ackInvSet: out std_logic;<br>ackInvSet: in std_logic;<br>ackInvSet: in std_logic;<br>ackInvSet: out st            | lybd      |           |                                                                                                       |

| v1_0vhd     30     movetoAngle: in std_logic_vector(15 downto 0);       u_0vhd     31     movetoTstep: in std_logic;       32     reqInvSet: in std_logic;       33     reqInvSet: in std_logic;       34     ackInvSet: out std_logic;       35     setEng: in std_logic_vector(7 downto 0);       36     setFing: in std_logic_vector(7 downto 0);       37     setCoNctor: in std_logic;       38     setTstep: in std_logic;       39     reqInvZero: in std_logic;       40     step1: out std_logic;       41     ackInvZero: out std_logic;       42     step2: out std_logic;       43     step2: out std_logic;       44     step2: out std_logic;       45     step3: out std_logic;       46     step2: out std_logic;       59     end Step;       51     architecture Step of Step is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |           | 27 reqInvMoveto: in std_logic;                                                                        |

| v1_0vhd         38         novet0Angle: in std_logic_vector(15 downto 0);<br>novet0Angle: in std_logic_vector(7 downto 0);           L_0vhd         32         reqInvSet: in std_logic;           33         ackInvSet: out std_logic;           34         ackInvSet: out std_logic;           35         setEng: in std_logic_vector(7 downto 0);           36         setEng: in std_logic_vector(7 downto 0);           37         setEcxWortCv: in std_logic;           38         setTiste: in std_logic;           39         reqInvZero: in std_logic;           40         43         step1: out std_logic;           41         ackInvZero: out std_logic;           42         step1: out std_logic;           43         step1: out std_logic;           44         step2: out std_logic;           45         step3: out std_logic;           46         stateOp_dog: out std_logic;           47         stateOp_dog: out std_logic;           48         stateOp_dog: out std_logic;           49         );         stateOp_dog: out std_logic;           51         architecture Step of Step is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |           |                                                                                                       |

| v1_0.vhd     31     movetoTstep: in std_logic_vector(7 downto 0);       L_0.vhd     32     reqInvSet: in std_logic;       33     ackInvSet: out std_logic;       34     ackInvSet: out std_logic,       35     setRng: in std_logic,vector(7 downto 0);       36     setTstep: in std_logic,vector(7 downto 0);       37     setCsNctOx: in std_logic,vector(7 downto 0);       38     setTstep: in std_logic;       40     reqInvZero: in std_logic;       41     ackInvZero: out std_logic;       42     step1: out std_logic;       43     step2: out std_logic;       44     step2: out std_logic;       45     step4: out std_logic;       46     step2: out std_logic;       47     stateDp_dbg: out std_logic;       48     stateDp_dbg: out std_logic;       59     end Step;       51     architecture Step of Step is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |           |                                                                                                       |

| LOxhd         32         reaInvSet: in std_logic;           33         ackInvSet: out std_logic;           34         ackInvSet: out std_logic;           35         setEng: in std_logic_vector(7 downto 0);           36         setEration is std_logic_vector(7 downto 0);           37         setEration is std_logic_vector(7 downto 0);           38         setTstep: in std_logic_vector(7 downto 0);           39         reqInvZero: in std_logic;           40         43         step1: out std_logic;           41         ackInvZero: out std_logic;           42         step1: out std_logic;           43         step1: out std_logic;           44         step2: out std_logic;           45         step3: out std_logic;           46         stateOp_ddg: out std_logic;           47         stateOp_ddg: out std_logic;           50         end Step;           51         architecture Step of Step is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _v1_0.vhd |           |                                                                                                       |

| 34         ackInvSet: out std_logic;           35         setRop: in std_logic_vector(7 downto 0);           36         setRop: in std_logic_vector(7 downto 0);           37         setConvCrist in std_logic_vector(7 downto 0);           38         setTstep: in std_logic;           40         reqInvZero: in std_logic;           41         ackInvZero: out std_logic;           42         step1: out std_logic;           43         step1: out std_logic;           44         step2: out std_logic;           45         step3: out std_logic;           46         stateOp_ddg: out std_logic;           47         stateOp_ddg: out std_logic;           68         stateOp_ddg: out std_logic;           69         end Step;           51         architecture Step of Step is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.vhd     |           |                                                                                                       |

| 35       35         36       setRap: in std_logic_vector(7 downto 0);         37       setCoMiot(w: in std_logic_vector(7 downto 0);         38       setTstep: in std_logic_vector(7 downto 0);         39       reqInvZero: in std_logic;         40       reqInvZero: out std_logic;         41       ackInvZero: out std_logic;         42       step1: out std_logic;         43       step2: out std_logic;         44       step2: out std_logic;         45       step4: out std_logic;         46       step4: out std_logic;         47       stateDp_dbg: out std_logic;         48       stateDp_dbg: out std_logic,         99       );         90       end Step;         91       architecture Step of Step is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _         |           |                                                                                                       |